Linux auf Quad-Core-RISC-V-Prozessor mit 64 bit

SiFive hat eine Open-Source-RISC-V-Architektur für einen Quad-Core-Prozessor für komplette Betriebssysteme wie Linux freigegeben. Laut SiFive markiert „die Veröffentlichung des U54-MC Coreplex die Erweiterung der Architektur in Richtung von Anwendungsprozessoren und eröffnet so völlig neue Anwendungen für RISC-V. Diese Lösung ist ideal für Anwendungen, die ein vollständiges Betriebssystem benötigen, wie etwa KI, maschinelles Lernen, Netzwerke, Gateways und intelligente IoT-Geräte.“

SiFive hat eine Open-Source-RISC-V-Architektur für einen Quad-Core-Prozessor für komplette Betriebssysteme wie Linux freigegeben. Laut SiFive markiert „die Veröffentlichung des U54-MC Coreplex die Erweiterung der Architektur Richtung Anwendungsprozessoren und eröffnet so völlig neue Anwendungen für RISC-V. Diese Lösung ist ideal für Anwendungen, die ein vollständiges Betriebssystem benötigen, wie etwa KI, maschinelles Lernen, Netzwerke, Gateways und intelligente IoT-Geräte.“

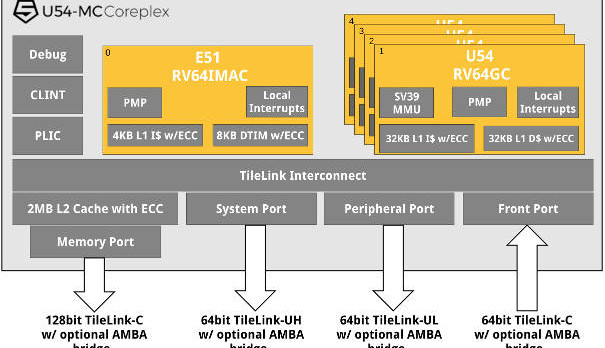

Ein Standard-U54-MC enthält vier U54-Kerne zusammen mit einem einzelnen E51-Kern und unterstützt Cache-Kohärenz. Jeder U54-Core verfügt über eine fünfstufige In-Order-Pipeline und unterstützt RV64GC ISA. Der 64-bittige E51-CCorePU dient als Manager und ist voll kohärent zu den U54-Kernen.

U54-MC Coreplex wurde als Teil der „Freedom Unleashed“-Familie von SiFive mit anpassbaren RISC-V-SoCs aufgenommen. Die CPUs U54 und E51 dieser Plattform sind in 28-nm-Strukturen gefertigt und operieren mit einem Takt von >1,5 GHz. Jeder U54-Core verfügt über einen 32-KB-Befehls-Cache und einen 32-KB-Daten-Cache. Alle Kerne teilen sich einen kohärenten 2-MB-Level-2-Cache.

Kunden können den U54-MC Coreplex in einer Vielzahl von Konfigurationen neben der 4 + 1 Standardkonfiguration lizenzieren.

Ein Entwicklungsboard wird im ersten Quartal nächsten Jahres zur Verfügung stehen.

Ein Standard-U54-MC enthält vier U54-Kerne zusammen mit einem einzelnen E51-Kern und unterstützt Cache-Kohärenz. Jeder U54-Core verfügt über eine fünfstufige In-Order-Pipeline und unterstützt RV64GC ISA. Der 64-bittige E51-CCorePU dient als Manager und ist voll kohärent zu den U54-Kernen.

U54-MC Coreplex wurde als Teil der „Freedom Unleashed“-Familie von SiFive mit anpassbaren RISC-V-SoCs aufgenommen. Die CPUs U54 und E51 dieser Plattform sind in 28-nm-Strukturen gefertigt und operieren mit einem Takt von >1,5 GHz. Jeder U54-Core verfügt über einen 32-KB-Befehls-Cache und einen 32-KB-Daten-Cache. Alle Kerne teilen sich einen kohärenten 2-MB-Level-2-Cache.

Kunden können den U54-MC Coreplex in einer Vielzahl von Konfigurationen neben der 4 + 1 Standardkonfiguration lizenzieren.

Ein Entwicklungsboard wird im ersten Quartal nächsten Jahres zur Verfügung stehen.