HDI der Mittelklasse

über

Ein neuer ökonomischer PCB Pooling Service für hochpolige BGAs

Manchmal gibt es das Bauteil, das wir unbedingt für unser Projekt verwenden möchten, nur in einem Fine-Pitch-BGA-Gehäuse. Das bedeutet, dass unser Design die Grenze der Standardleiterplattentechnik in den HDI-Bereich überschreitet. Technisch gesehen bedeutet HDI High Density Interconnect und praktisch, dass wir mit kleineren Abständen und feineren Leiterbahnen layouten können. Außerdem können wir Microvias verwenden – Durchkontaktierungen mit kleineren Pads und kleineren Durchmessern, als es normalerweise mit mechanischen Bohrungen möglich ist.

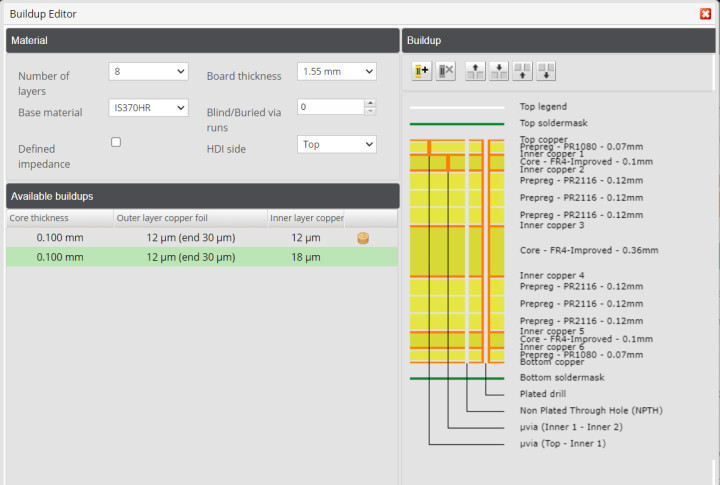

HDI ermöglicht die Miniaturisierung. Das ist großartig, kann aber lästig sein, wenn sie uns durch ein einziges Bauteil auf die gesamte Leiterplatte „gezwungen“ wird, die sich dadurch verteuert. Bei Eurocircuits haben wir eine “Mittelklasse”-Lösung, mit der man sowohl das Bauteil als auch die Kosten unter einen Hut bringen kann. Unser HDI-Pool (Bild 1), ein 8-Lagen-Aufbau, behält die Leiterbildklassen der Standardtechnologie bei und fügt Mikrovias zwischen den Lagen 1-2 und 2-3 oder 8-7 und 7-6 hinzu, nur nicht beide. Dadurch können unsere Kunden diese Fine-Pitch-BGAs entflechten und die Kosten sind überschaubar, weil HDI nur auf einen kleinen Bereich und zwei Microvia-Lagen beschränkt ist.

In der Praxis

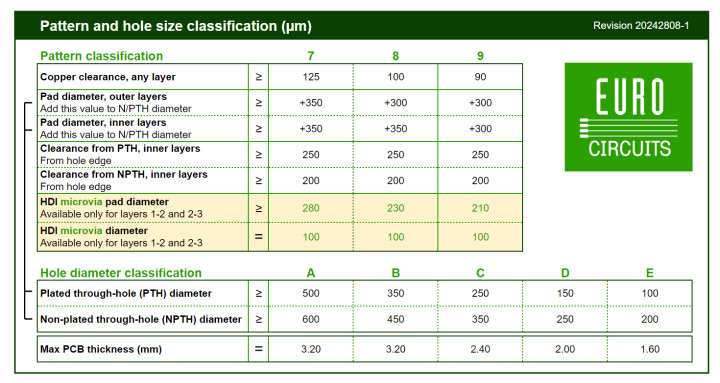

Was heißt das in der Praxis? Betrachten wir die Leiterbildklasse 7 mit der Bohrklasse E in Bild 2. Der kleinstmögliche Pad-Durchmesser beträgt 0,45 mm (0,1 + 0,35 mm). Das passt nicht in die meisten Fine-Pitch-BGA-Pads. Wenn wir jedoch dieselbe Klasse zusammen mit dem HDI-Pool verwenden, beträgt der kleinste Durchmesser 0,28 mm und passt! PCB-Designer können damit Vias in der Mitte von BGA-Pads platzieren, ohne die Pads über die Empfehlungen des Herstellers hinaus vergrößern zu müssen. Die kleineren Microvia-Pads ermöglichen zudem Dogbone-Anschlüsse.

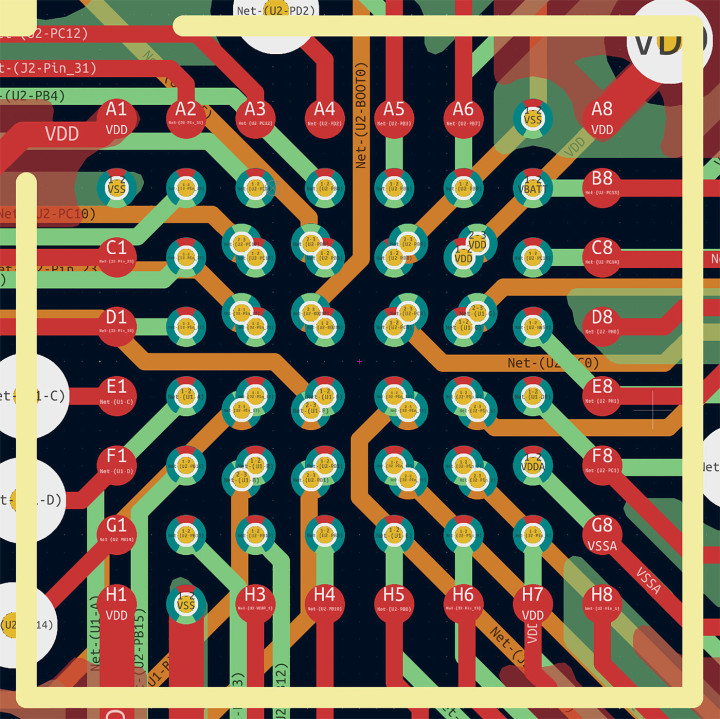

Es ist unmöglich, alle BGA-Pin-Arrays und ihre Pin-Konfigurationen zu berücksichtigen, um festzustellen, welches Bauteil geroutet werden kann und welches nicht. Trotzdem haben wir unsere Pool-Parameter so konfiguriert, dass vollständige 8x8-Arrays für BGAs bis zu 0,4 mm Pitch vollständig geroutet werden können. Bild 3 zeigt ein Beispiel für ein vollständig aufgefächertes 8x8-Bauteil mit 0,4 mm Raster. Selbstverständlich sind auch größere Arrays möglich, und alles hängt von der Array-Größe, der Pin-Konfiguration und der Art der Verwendung dieser Pins ab. In vielen Gehäusen gibt es No-Connect-Pins, und in den meisten Designs werden nicht alle Pins des Mikrocontrollers oder Prozessors verwendet. Das kann das Entflechten großer BGA-Arrays mit nur zwei Microvia-Lagen erleichtern.

Jetzt kommen Sie! Laden Sie Ihr Design in unseren Visualizer hoch und prüfen Sie es auf Fertigbarkeit! Wie immer freuen wir uns über Ihr Feedback, wie dieser Service Ihre Arbeit unterstützt.

Diskussion (0 Kommentare)