Neue CPLD-Platine mit MAX10 – Mehr Logik mit der MAX10-Familie

16. April 2019

über

über

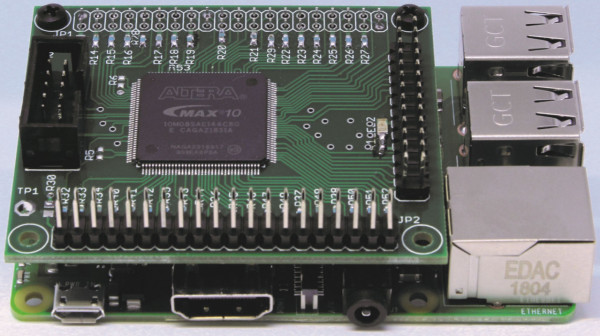

In Elektor 5-6/2018 stellte der Autor eine Platine mit einem CPLD aus der MAX-II-Familie von Altera (heute: Intel) vor. Der damals verwendete EPM570 ist ein CPLD mit 570 Logik-Elementen (LE) in einem TQFP100-Gehäuse, auch der kleinere, aber pinkompatible EPM240 konnte auf der CPLD-Platine eingesetzt werden. Durch dieses relativ kleine Bauteilgehäuse war es möglich, eine Prototypen-Platine so zu gestalten, dass das IC quasi wie ein DIL-IC verwendet werden konnte.

Zwar kann man mit 570 LE schon eine ganze Menge Logik aufbauen, doch wenn sie nicht ausreichen, muss man auf eine andere CPLD-Familie zurückgreifen. Da die MAX-V-Reihe nur wenige Vorteile gegenüber der MAX-II-Familie bringt, warum also nicht direkt Intels aktuelle CPLD-Familie MAX 10 nutzen? Die Familie besteht aus sieben CPLD-Produktgruppen, jeweils in diversen Varianten. Man hat die Wahl: 2 k bis 50 k Logikelemente, einfache oder duale Spannungsversorgung mit integriertem 3,3-V-LDO (wobei bei dem verwendeten Modell nur Single Power Supply möglich ist), verschiedene Flash-Speicherblockgrößen, Analog-Digital-Wandler (ADCs), Temperatursensor, Dual Configuration Flash (zwei dynamisch nutzbare Images auf einem Chip) und vieles mehr.

Vom CPLD zum FPGA

Die MAX-10-Familie besitzt auch über reine CPLD-Funktionen hinausgehend voll funktionsfähige FPGA-Funktionen wie (bis zu vier) interne PLLs , um höhere Taktraten zu erzeugen, implementierbare (NIOS-)Mikrocontroller, DSP-Blöcke (Digital Signal Processing) und Soft-DDR3-Speichersteuerungen.All diese verschiedenen Varianten stehen in etlichen Gehäusebauformen (vom kleinen Wafergehäuse bis zu großen Gehäusen mit hunderten von I/O-Pins) zur Verfügung. Dies ist auch schon unser erstes Auswahlkriterium: Das einzige für Amateure (das heißt, mit einem Lötkolben) noch lötbare Gehäuse ist nämlich ein EQFP mit 144 Anschlüssen. Durch dieses 22x22 mm2 große Gehäuse fällt die Platine zwar etwas größer als das Vorgängermodell, bietet dafür aber auch (in allen Varianten) 101 nutzbare IOs. Mehr und detaillierte Informationen bietet das Handbuch der MAX-10-Familie.

Peripherie

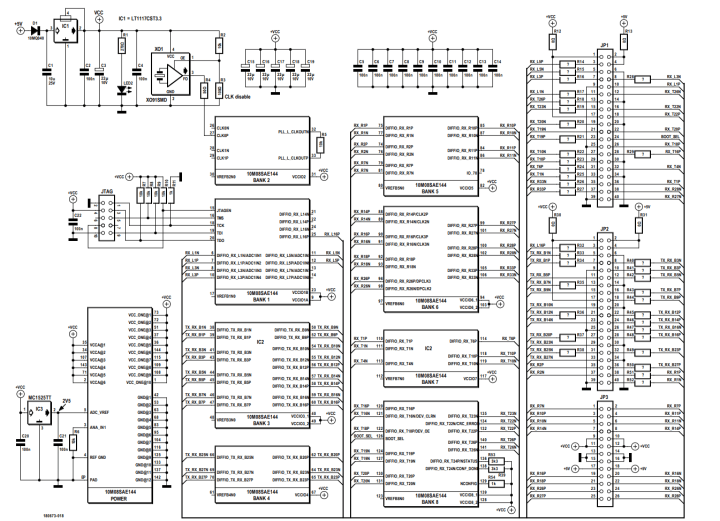

Wie auch der kleinere Vorgänger beherbergt auch diese Platine, wie der Schaltplan in Bild 1 zeigt, neben dem neuen CPLD auch einen Spannungsregler inklusive Abblockkondensatoren, einen Taktoszillator und den JTAG-Stecker zum Programmieren. Zusätzlich an Board ist eine Spannungsreferenz für den im CPLD integrierten A/D-Wandler (Bank 1A).

Der Prototyp ist mit einem 10M08 bestückt, der 8 K Logikeinheiten (LE), eine PLL und einen A/D-Wandler besitzt. Die Platine ist aber für alle Mitglieder der MAX-10-Familie mit 2...50 K LEs geeignet, sofern sie in einem EQFP-144-Gehäuse stecken. Das Layout der Platine weist wieder vier Lagen auf, damit die sichere Funktionsweise auch bei höheren Taktraten gewährleistet ist.

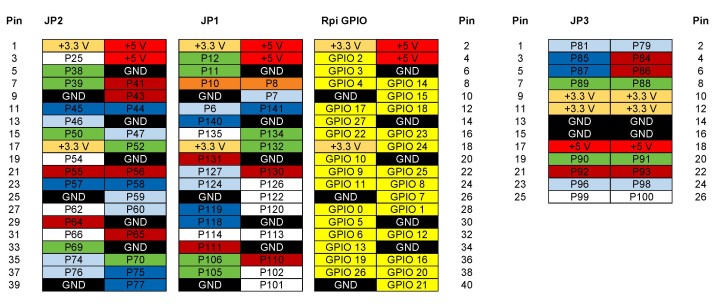

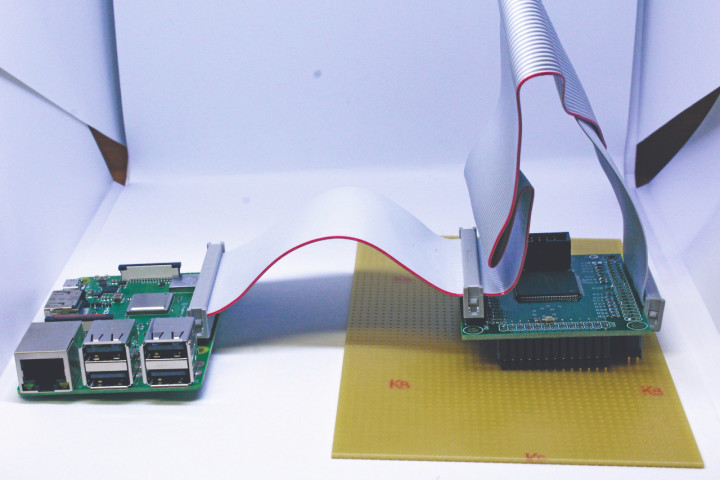

Wie auch beim Vorgängermodell sind auch hier nicht alle möglichen I/Os auf die Verbinder geführt, und zwar aus gutem Grund: Das Board kann zwar wie ein großes DIL-IC auf einem Steckboard oder einer Lochraster-Platine benutzt werden, der eigentliche Clou aber ist, dass die beiden (!) langen Stift/Buchsenleisten die gleiche Pinbelegung wie der 2x20-polige IO-Stecker eines Raspberry Pi (ab Version 2) aufweisen und somit direkt auf den Minirechner aufgesteckt werden können. Damit kombiniert man die Rechenleistung und die PC-Schnittstellen des Raspberry Pi mit den Hardwaremöglichkeiten eines modernen CPLDs. In Bild 2 ist die Belegung der drei Verbinder (mit den Pins des CPLDs) und zum Vergleich der GPIO-Stecker des Raspberry Pi zu sehen. Nebeneinander liegende, mit jeweils der gleichen Farbe versehene Anschlüsse bilden ein differenzielles Ein- oder Ausgangspaar, die, wie alle nicht eingefärbten Anschlüsse, natürlich auch „single“ benutzt werden können.

Kombinationen

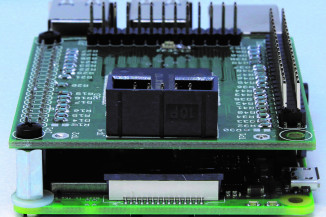

Auch die Befestigungslöcher passen.

Bild 4 zeigt, wie der RPi über JP2 den CPLD und dieser über JP1 die Elektronik (zum Beispiel Leistungstreiber) auf einer Lochrasterplatine steuert. Man kann die Stromversorgung der beiden Platinen koppeln oder getrennt halten. Dafür sind 0-Ω-Widerstände R12, R13, R30 und R31 vorgesehen.

Wer zuerst kommt...

Beim Autor alfred_rosenkraenzer@gmx.de sind einige wenige Leer- und teilbestückte Platinen erhältlich (CPLD MAX 10 ist bestückt, sonst nichts).Im Elektor-Shop ist das teilbestückte CPLD-Breakout-Board mit CPLD MAX II (Projekt aus 5-6/2018) erhältlich.

(180673)

➔ Wollen Sie weitere ElektorLabs-Artikel lesen? Jetzt Elektor-Mitglied werden!

Mehr anzeigen

Weniger anzeigen

Diskussion (2 Kommentare)