Parallax Propeller 2

über

Als Parallax 2006 seinen ersten Propeller-Chip vorstellte, war das etwas völlig anderes als alles, was wir zuvor gesehen hatten. Seit einigen Monaten arbeitet Parallax an der neuen Version 2 des Chips, und zwar auf eine ungewöhnliche Art. Der neue Propeller wurde zunächst nicht als fertiger Silizium-Chip, sondern lediglich als Bitstream für ein DE10-Nano FPGA-Board von Altera eingeführt, mit der Bitte an User und Ingenieure um Feedback. Im Laufe der Zeit sammelte Parallax das Feedback und erhielt so wichtige Kriterien für den Bau des „echten“ Propeller 2 in Silizium. Das Unternehmen berichtete zudem in einem Propeller-Forum fortwährend über den Prozess der Chip-Herstellung, so dass die Community immer auf den neusten Stand bleib. Während ich dies hier schreibe, wird der Silizium-Chip in der Revision C für die Produktion freigegeben. Werfen wir also einen Blick auf den Propeller 2 und seine Eigenschaften!

Der Propeller 2

Der Chip ist offiziell für eine Taktfrequenz von 180 MHz ausgelegt, was zu 90 MIPS pro Kern führt, und jeder Befehl benötigt mindestens zwei Taktzyklen. Eine Übertaktung des Propeller 2 bis mehr als 300 MHz ist möglich, so dass eine Rechenleistung von 150 MIPS pro Kern erreicht werden kann. Normalerweise besitzt ein Mikrocontroller einen Kern oder zwei, beim Propeller 2 sind es dagegen acht unabhängige Kerne, die so genannten Cogs, die eine Menge Rechenleistung liefern. Alle Cogs teilen sich bei diesem Modell 512 KB RAM sowie zusätzliche 512 * 32 Bit-Register und 512 * 32 Bit Lookup-RAM pro Kern. Neben der Zahl der Kerne und dem RAM enthält der Chip eine ganze Reihe interessanter Peripherie und Funktionen:

- CORDIC-Solver mit Skalierungsfaktor-Korrektur

- 16 Semaphor-Bits mit atomarem Read-Modify-Write (RMW)

- Frei laufender 64-Bit-Zähler

- USB 2.0-FS-Host- und Slave-Interface

- Intelligente I/O-Pins (Einzelheiten im Kasten „Intelligente Pin-Funktionen“).

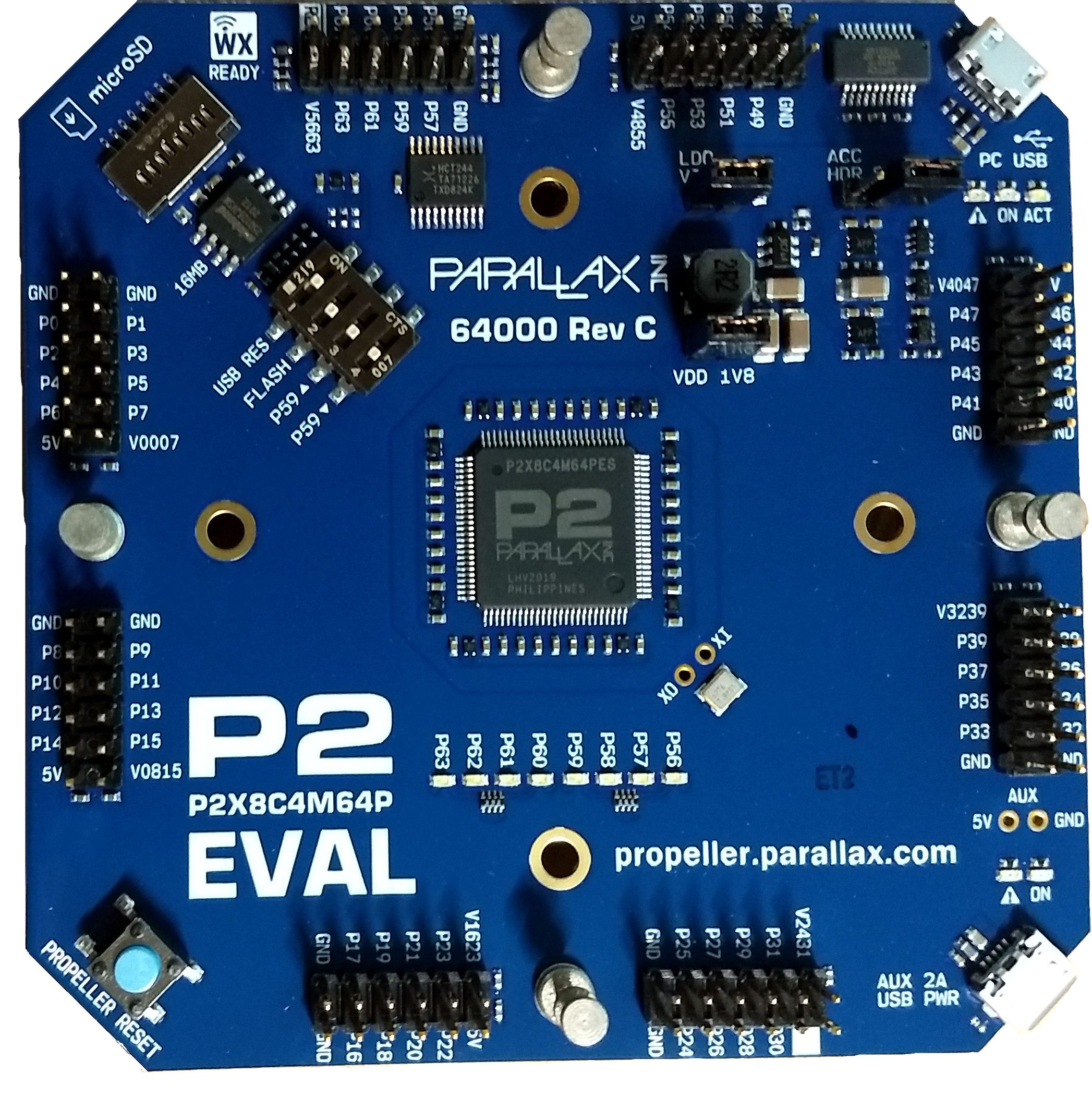

Parallax war so freundlich, uns ein Evaluation-Kit (Bild 1) mit einem Controller der der Revision C zu überlassen, damit wir einen ersten Blick darauf werfen können.

In dieser Artikelserie werden wir den Chip, seine Peripherie, Beispielcode und mehr genau unter die Lupe nehmen.

Eine kleine Warnung: Während ich dies schreibe, ist der Chip offiziell noch nicht freigegeben, so dass Sie damit rechnen müssen, dass wir auf einige „Unebenheiten“ in der Software stoßen werden. Uns wurde nicht nur das blanke Evaluation-Board zur Verfügung gestellt, sondern auch ein Stapel von Add-Ons (siehe Bild 2), der eine Vielzahl von Tests und Spielereien bequem gestaltete.

Wo ist die Peripherie geblieben?

Sie fragen sich, wo die SPI-, I2C- und UART-Module geblieben sind? Diese können mit Hilfe der Smart-Pins und etwas Code innerhalb der Cogs gebildet werden, und auch wenn sie nicht direkt in der Feature Map stehen sind, sind sie verfügbar. Mit diesem Ansatz werden wir (am Ende der Artikelreihe) in der Lage sein, ein HDMI-Signal direkt auf einen Monitor auszugeben und Inhalte von einem Flash-Chip anzuzeigen. Da eine Beschreibung der einzelnen Peripherieeigenschaften „am Stück“ recht langwierig und langweilig wäre, wollen wir sie im Laufe der Artikelserie bei Bedarf vornehmen. Im nächsten Teil des Artikels werden wir einen kurzen Blick auf die Entwicklungsumgebung werfen und mit unserem ersten I/O-Pin eine LED ansteuern.

Want more great Elektor content like this?

► Take out an Elektor membership today and never miss an article, project, or tutorial.

Diskussion (0 Kommentare)